# Implement I281 CPU

DESIGN DOCUMENT

Team Number: sddec22-20 Client: Dr. Alexander Stoytchev Advisor(s): Dr. Alexander Stoytchev Team Members/Roles Alex Kiefer/Group Lead and Lead Hardware Joseph De Jong/Hardware Testing, Communications, and Reporting David Vachlon/Purchasing Lead, Software Testing, and Hardware Testing Lead Saffron Edwards/Lead Software, Software Testing, and Website Maintenance Patrick O-Brien/Documentation, Progress Reports, and Meeting Notes Team Email: sddec22-20@iastate.edu Team Website: https://sddec22-20.sd.ece.iastate.edu/

Revised: 4/24/2022

# **Executive Summary**

# Development Standards & Practices Used

List all standard circuit, hardware, software practices used in this project. List all the Engineering standards that apply to this project that were considered.

# Engineering Standards:

- 1012-2016 IEEE Standard for System, Software, and Hardware Verification and Validation: We need this standard in order to test hardware and Professor Stoytchev's ISA (instruction set architecture) on our computer.

- 370-2020 IEEE Standard for Electrical Characterization of Printed Circuit Board and Related Interconnects at Frequencies up to 50 GHz: We need this standard in order to make sure that we make our PCB of the high quality Professor Stoytchev expects.

- 162-1963 IEEE Standard Definitions of Terms for Electronic Digital Computers: We need this standard in order to make sure that the pcb we build for students uses the correct names for its components. Because this will be used in a learning environment, it is essential that we do not lead students.

# Summary of Requirements

- Must be visual so that students can learn

- Must be Reprogrammable

- Use less than 50W of power

- Must be able to run all of Dr. Stoytchev's ISA instructions

# Applicable Courses from Iowa State University Curriculum

Cpre 281

Cpre 381

EE 201 EE 230

# New Skills/Knowledge acquired that was not taught in courses

How to program EEproms

KiCad

# Table of Contents

| Engineering Standards:                                            | 1  |

|-------------------------------------------------------------------|----|

| Summary of Requirements                                           | 1  |

| Applicable Courses from Iowa State University Curriculum          | 1  |

| New Skills/Knowledge acquired that was not taught in courses      | 2  |

| 1. Team                                                           | 6  |

| 1.1 Team Members                                                  | 6  |

| 1.2 Required Skill Sets for Your Project                          | 6  |

| 1.3 Skill Sets covered by the Team                                | 6  |

| 1.4 Project Management Style Adopted by the team                  | 6  |

| 1.5 Initial Project Management Roles                              | 7  |

| 2. Introduction                                                   | 7  |

| 2.1 Problem Statement                                             | 7  |

| 2.2 Requirements & Constraints                                    | 7  |

| 2.3 Engineering Standards                                         | 9  |

| 2.4 Intended Users and Uses                                       | 9  |

| 3. Project Plan                                                   | 10 |

| 3.1 Project Management/Tracking Procedures                        | 10 |

| 3.2 Task Decomposition                                            | 11 |

| 3.3 Project Proposed Milestones, Metrics, and Evaluation Criteria | 12 |

| 3.4 Project Timeline/Schedule                                     | 13 |

| 3.5 Risks And Risk Management/Mitigation                          | 14 |

| 3.6 Personnel Effort Requirements                                 | 15 |

| 3.7 Other Resource Requirements                                   | 17 |

| 4 Design                                                          | 18 |

| 4.1 Design Context                                                | 18 |

| 4.1.1 Broader Context                                             | 18 |

| 4.1.2 User Needs                                                  | 20 |

| 4.1.3 Prior Work/Solutions                             | 20 |

|--------------------------------------------------------|----|

| 4.1.4 Technical Complexity                             | 21 |

| 4.2 Design Exploration                                 | 22 |

| 4.2.1 Design Decisions                                 | 22 |

| 4.2.2 Ideation                                         | 23 |

| 4.2.3 Decision-Making and Trade-Off                    | 23 |

| Proposed Design                                        | 24 |

| 4.3.1 Design Visual and Description                    | 24 |

| 4.3.2 Functionality                                    | 25 |

| 4.3.3 Areas of Concern and Development                 | 25 |

| 4.4 Technology Considerations                          | 26 |

| 4.5 Design Analysis                                    | 26 |

| 4.6 Design Plan                                        | 27 |

| 5 Testing                                              | 27 |

| 5.1 Unit Testing                                       | 27 |

| 5.2 Interface Testing                                  | 28 |

| 5.3 Integration Testing                                | 28 |

| System Testing                                         | 28 |

| Regression Testing                                     | 28 |

| Acceptance Testing                                     | 29 |

| Results                                                | 29 |

| 6 Implementation                                       | 29 |

| 7 Professionalism                                      | 30 |

| 7.1 Areas of Responsibility                            | 30 |

| 7.2 Project Specific Professional Responsibility Areas | 33 |

| 7.3 Most Applicable Professional Responsibility Area   | 34 |

| 8 Closing Material                                     | 35 |

| 8.1 Discussion                                         | 35 |

| 8.2 Conclusion      | 35 |

|---------------------|----|

| 8.3 References      | 36 |

| 8.4 Appendices      | 36 |

| 8.4.1 Team Contract | 36 |

# List of figures/tables/symbols/definitions

- 1) ISA : Instruction Set Architecture

- 2) CPU: Central Processing Unit

- 3) PCB: Printed Circuit Board

- 4) Breadboard: Board used to Prototype Circuits

- 5) LED: Light Emitting Diode

- Assembly Language: The Lowest Level form of Programming, an Assembly Language consists of only 1's and 0's

- 7) OPCODE: An OPCODE is the Name for an Instruction Written in Assembly

- 8) ALU: The Arithmetic Logic Unit

- 9) EEPROM: Electrically Erasable Programmable Read-Only Memory

# 1 Team

## 1.1 TEAM MEMBERS

- 1) David Vachlon

- 2) Saffron Edwards

- 3) Alex Kiefer

- 4) Patrick O'Brien

- 5) Joseph De Jong

# 1.2 Required Skill Sets for Your Project

<u>Electrical Engineering</u> - The majority of this project will be Electrical Engineering focused. Students will work with their team to research and implement various devices to build a working i281 CPU on breadboards.

<u>Computer Engineering</u> - After completing the building phase, Computer Engineering will be used to implement a custom ISA onto the CPU to run a variety of programs.

<u>Software Engineering</u> - Software Engineering will be used throughout the course of the project to write test benches that will be used to test the functionality of the CPU and the ISA.

# 1.3 Skill Sets covered by the Team

Electrical Engineering - Patrick O'Brien, Alex Kiefer, Joseph De Jong

Computer Engineering - David Vachlon

Software Engineering - Saffron Edwards

## 1.4 Project Management Style Adopted by the team

Our project management style is waterfall. We will focus on completing a full stage before moving onto the next phase. This is important because we will be creating a PCB and PCBs are very costly if mistakes are made. It is because of this that it is essential to create a fully working prototype and get approval for printing before ordering the fully functional PCB. On top of saving money, waterfall will help us save time. Computers are built one module at a time and by having the entire team focused on distinct modules it will help us avoid mistakes that could cost us valuable time for troubleshooting later on in the project.

## 1.5 INITIAL PROJECT MANAGEMENT ROLES

Alex Kiefer - Group Lead and Lead Hardware

Joseph De Jong - Hardware Testing, Communications, and Reporting David Vachlon - Purchasing Lead, Software Testing, and Hardware Testing Lead Saffron Edwards - Lead Software, Software Testing, and Website Maintenance Patrick O-Brien - Documentation, Progress Reports, and Meeting Notes

# 2 Introduction

# 2.1 PROBLEM STATEMENT

## What problem is your project trying to solve? Use non-technical jargon as much as possible.

The College of Electrical and Computer Engineering at Iowa State offers programs that help to describe hardware and software to its students. However it seems that Iowa State, and many other universities around the country, lack material that effectively builds the connection between hardware and software with undergraduate students. Teaching Professor Alexander Stoytchev is seeking to bridge that gap by developing an easily understandable hardware implementation of a simple computer processor. Past senior design groups have developed an online simulation of the processor, but the professor wants a hardware implementation to prove that the design actually works in the real world. The current issue is to prove that the design works by using breadboards to implement each subcomponent of the computer, and resolve any issues with the current design. Once a design has been built and comprehensively tested using breadboards, we will design a pcb (printed circuit board) for the professor to use during lectures and labs.

# 2.2 Requirements & Constraints

List all requirements for your project. This includes functional requirements (specification), resource requirements, qualitative aesthetics requirements, economic/market requirements, environmental requirements, UI requirements, and any others relevant to your project. When a requirement is also a quantitative constraint, either separate it into a list of constraints, or annotate at the end of requirement as "(constraint)". Other requirements can be a single list or can be broken out into multiple lists based on the category.

| Requirements                   | Constraints                   |

|--------------------------------|-------------------------------|

| CPU must be able to execute an | Building our project first on |

| instruction every clock cycle.                                         | breadboards makes it much more<br>difficult to implement since we really<br>have to keep this requirement in mind<br>as we build each component. Building<br>one component incorrectly would result<br>in this requirement not being met.                                            |

|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Must have a variable speed clock                                       | Confined to low power and through hole chips due to chip availability.                                                                                                                                                                                                               |

| Must be programmable                                                   | We are limited by a 5 volt power supply,<br>which means we have a lot that this<br>computer needs to be able to do with a<br>limited amount of power.                                                                                                                                |

| Must run preset programs including<br>Pong and Bubble Sort             | Another constraint for this project is<br>that we must use 22awg solid core wire<br>for all connections, which means that<br>we need to have a specific item in stock<br>for us and cannot vary from it.Confined<br>to low power and through hole chips<br>due to chip availability. |

| Must be broken up into easy to<br>understand modules                   | A technical constraint for us is that<br>Stoytchev's design uses a 16 bit<br>instruction memory and 8 bit data<br>memory. This means that we have to<br>get clever with our implementation due<br>to these big differences.                                                          |

| Must display output on 7-seg display or<br>LEDs                        | The completed project is due by December 2022.                                                                                                                                                                                                                                       |

| Must include user inputs involving slide<br>switches and push buttons  | Breadboard implementation is slow to test and incredibly error prone.                                                                                                                                                                                                                |

| Breadboard implementation must be<br>functional first due to pcb costs | Limited budget (only get 1 or 2<br>attempts at printing a pcb so we have to<br>get it right).                                                                                                                                                                                        |

| Must run commands based on<br>Professor Stoytchev's assembly language  | We are not entirely sure how to program the CPU yet.                                                                                                                                                                                                                                 |

| Must be portable                                                       | The PCB needs to be very visual so<br>students can learn but at the same time<br>portable, which means it can't be too                                                                                                                                                               |

|                                                                        | large.                                                                                                            |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Must easily demonstrate progress of a program throughout its execution | LEDS must be placed at carefully<br>thought out locations on the pcb to<br>convey useful information to students. |

| Create functional implementation of the i281 CPU on hardware           | We are constrained by lack of experience in building a CPU.                                                       |

## 2.3 Engineering Standards

What Engineering standards are likely to apply to your project? Some standards might be built into your requirements (Use 802.11 ac wifi standard) and many others might fall out of design. For each standard listed, also provide a brief justification.

| Engineering Standard                                                                                                                             | Justification                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1012-2016 - IEEE Standard for System,<br>Software, and Hardware Verification and<br>Validation - Redline                                         | We need this standard in order to test<br>hardware and Professor Stoytchev's ISA<br>(instruction set architecture) on our<br>computer.                                                                                                                                                                             |

| 370-2020 - IEEE Standard for Electrical<br>Characterization of Printed Circuit Board<br>and Related Interconnects at Frequencies<br>up to 50 GHz | We need this standard in order to make sure<br>that we make our PCB of the high quality<br>Professor Stoytchev expects.                                                                                                                                                                                            |

| 162-1963 - IEEE Standard Definitions of<br>Terms for Electronic Digital Computers                                                                | We need this standard in order to make sure<br>that the pcb we build for students uses the<br>correct names for its components. Because<br>this will be used in a learning environment,<br>it is essential that we do not lead students<br>astray and only use terms and names that<br>they would see in industry. |

# 2.4 INTENDED USERS AND USES

Who benefits from the results of your project? Who cares that it exists? How will they use it? Enumerating as many "use cases" as possible also helps you make sure that your requirements are complete (each use case may give rise to its own set of requirements).

Both Professor Stoytchev and his students benefit from the successful implementation of this project. This is because this will be used to enhance the learning experience of future undergrads in the ECpE program here at Iowa State. Additionally, this project should cause a greater number of students to feel as though they have mastered the material, which should help them in future courses. The only person who currently cares that this project exists is Professor Stoytchev.

This is because students who have already gone through his class won't be concerned about this project since it doesn't impact them and future students don't know about it and will only care once it is implemented.

This project will be used in the lab setting of CprE 281 to teach students how the different aspects of digital logic that they have learned all semester coalesce into a single, functional computing unit. They will interact with it by running programs through it and examining the output as well as by identifying the different components which comprise this computing system.

# 3. Project Plan

# 3.1 PROJECT MANAGEMENT/TRACKING PROCEDURES

Which of agile, waterfall or waterfall+agile project management style are you adopting? Justify it with respect to the project goals.

Our project management style is waterfall. We will focus on completing a full stage before moving onto the next phase. This is important because we will be creating a PCB and PCBs are very costly if mistakes are made. It is because of this that it is essential to create a fully working prototype and get approval for printing before ordering the fully functional PCB. On top of saving money, waterfall will help us save time. Computers are built one module at a time and by having the entire team focused on distinct modules it will help us avoid mistakes that could cost us valuable time for troubleshooting later on in the project.

# What will your group use to track progress throughout the course of this and the next semester. This could include Git, Github, Trello, Slack or any other tools helpful in project management.

The team will be utilizing 3 tools to track progress. The first tool our team implemented was a discord server. Through discord we are able to share information instantly while being able to see what each member is working on. On top of discord, we have a weekly progress report. In the weekly progress report each member writes up what they are currently working on and what their next step in the project is. This is a way for our team to document progress while seeing that no two team members are working on the exact same thing on accident. Finally, we have utilized meeting times to create a weekly

"to-do" list. This list is shared with the team members via the weekly progress reports and discord. This "to-do" list is meant as a quick stop to keep the team on track of what is due.

#### 3.2 TASK DECOMPOSITION

In order to solve the problem at hand, it helps to decompose it into multiple tasks and subtasks and to understand interdependence among tasks. This step might be useful even if you adopt agile methodology. If you are agile, you can also provide a linear progression of completed requirements aligned with your sprints for the entire project.

The i281 CPU will be broken down into 3 steps. The first step is to implement the i281 CPU onto a set of breadboards. Next, we test the breadboard CPU and design a schematic. Finally, we will design the CPU on a PCB and get it printed.

The first step, implementing the i281 CPU onto breadboards, will be the most tedious task and will be broken into subtasks. Each member will take on a subtask to lighten the load for everyone.

Our subtasks are as follows:

- 1. Instruction Memory

- 2. Registers

- 3. OpCode Decoder

- 4. ALU

- 5. Flags

- 6. Control

- 7. Multiplexors

- 8. Data Memory

- 9. Display

- 10. EEPROM Program

After each of these subtasks are implemented, we can begin testing. Testing will be broken down into subtasks of testing each instruction individually. The instruction set has 25 individual instructions that we will refrain from listing here to save space.

Finally, we will implement the CPU onto a PCB. The PCB implementation has three subtasks.

These subtasks are as follows:

- 1. Layout PCB using software

- 2. Print PCB

- 3. Solder devices onto PCB

After these three final subtasks are complete, the i281 CPU will be ready for use in a classroom setting.

# 3.3 PROJECT PROPOSED MILESTONES, METRICS, AND EVALUATION CRITERIA

What are some key milestones in your proposed project? It may be helpful to develop these milestones for each task and subtask from 2.2. How do you measure progress on a given task? These metrics, preferably quantifiable, should be developed for each task. The milestones should be stated in terms of these metrics: Machine learning algorithm XYZ will classify with 80% accuracy; the pattern recognition logic on FPGA will recognize a pattern every 1 ms (at 1K patterns/sec throughput). ML accuracy target might go up to 90% from 80%.

In an agile development process, these milestones can be refined with successive iterations/sprints (perhaps a subset of your requirements applicable to those sprints).

| Key Milestone                                 | Metrics                                                                                                                                                                                                                |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Implementation of every i281 CPU<br>component | Each individual CPU component completes<br>a testbench with 100% accuracy and the<br>device has been properly documented via<br>the progress report template.                                                          |

| Full implementation of the i281 CPU           | Each component of the i281 CPU has been<br>combined to create a working device. The<br>testbench has been passed with 100%<br>completion. The system has been fully<br>documented via the progress report<br>template. |

| Full PCB layout of the i281 CPU               | The schematics of the i281 CPU have been<br>transferred to the desired PCB design<br>software. The PCB layout passes all<br>geometry checks and is ready for printing.                                                 |

| Soldering of PCB | Upon arrival of the PCB, each device will<br>need to be soldered into place. The device<br>will need to pass all continuity checks.           |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Testing of PCB   | The i281 PCB will be tested on completion<br>of bubble sort and pong. Each program will<br>be required to be executed at 100%<br>correctness. |

# 3.4 Project Timeline/Schedule

• A realistic, well-planned schedule is an essential component of every well-planned project

• Most scheduling errors occur as the result of either not properly identifying all of the necessary activities (tasks and/or subtasks) or not properly estimating the amount of effort required to correctly complete the activity

• A detailed schedule is needed as a part of the plan:

- Start with a Gantt chart showing the tasks (that you developed in 2.2) and associated subtasks versus the proposed project calendar. The Gantt chart shall be referenced and summarized in the text.

- Annotate the Gantt chart with when each project deliverable will be delivered

• Project schedule/Gantt chart can be adapted to Agile or Waterfall development models. For agile, a sprint schedule with specific technical milestones/requirements/targets will work.

|                         | Date:     |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |            |            |            |            |           |

|-------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|------------|------------|------------|------------|-----------|

| Project:                | 2/15/2022 | 2/28/2022 | 3/15/2022 | 3/30/2022 | 4/15/2022 | 4/30/2022 | 5/15/2022 | 5/30/2022 | 6/15/2022 | 6/30/2022 | 7/15/2022 | 7/30/2022 | 8/15/2022 | 8/30/2022 | 9/15/2022 | 9/30/2022 | 10/15/2022 | 10/30/2022 | 11/15/2022 | 11/30/2022 | 12/15/202 |

| Registers               |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |            |            |            |            |           |

| OpCode Decoder          |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |            |            |            |            |           |

| ALU                     |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |            |            |            |            |           |

| Flags                   |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |            |            |            |            |           |

| Control                 |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |            |            |            |            |           |

| 7x Muxes                |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |            |            |            |            |           |

| Data Memory             |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |            |            |            |            |           |

| Display                 |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |            |            |            |            |           |

| EEPROM Program          |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |            |            |            |            |           |

| High Level Schematics   |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |            |            |            |            |           |

| Connect CPU             |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |            |            |            |            |           |

| Testbench CPU           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |            |            |            |            |           |

|                         |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |            |            |            |            |           |

| Layout PCB in software  |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |            |            |            |            |           |

| Print PCB               |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |            |            |            |            |           |

| Solder devices onto PCB | 3         |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |            |            |            |            |           |

| Testbench PCB           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |            |            |            |            |           |

# 3.5 RISKS AND RISK MANAGEMENT/MITIGATION

Consider for each task what risks exist (certain performance targets may not be met; certain tools may not work as expected) and assign an educated guess of probability for that risk. For any risk factor with a probability exceeding 0.5, develop a risk mitigation plan. Can you eliminate that task and add another task or set of tasks that might cost more? Can you buy something off-the-shelf from the market to achieve that functionality? Can you try an alternative tool, technology, algorithm, or board?

Agile projects can associate risks and risk mitigation with each sprint.

Unfortunately, none of these tasks can be eliminated due to the scope of our project. However, despite the risk associated with some of these tasks, there are tools that we can use/buy that will make implementing them more palatable.

| Tasks              | Risk Factor | Mitigation Plan                                                                                                                                                             |

|--------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction Memory | 0.5         | We can use SRAM in place<br>of the EEPROM that<br>professor Stoytchev<br>currently wants us to use if<br>we determine that<br>EEPROM will not be<br>effective in this role. |

| Registers          | 0.3         | N/A                                                                                                                                                                         |

| OpCode Decoder     | 0.3         | N/A                                                                                                                                                                         |

| ALU                | 0.1         | N/A                                                                                                                                                                         |

| Flags              | 0.1         | N/A                                                                                                                                                                         |

| Control Logic      | 0.21        | N/A                                                                                                                                                                         |

| Data Memory        | 0.7         | If we aren't able to<br>implement the Data<br>memory using EEPROM,<br>we will use SRAM or<br>general purpose registers as<br>an alternative.                                |

| Multiplexors       | 0.01        | N/A                                                                                                                                                                         |

| Display            | 0.3         | N/A                                                                                                                                                                         |

| EEPROM Program | 0.8 | If we are forced to use<br>EEPROM, we will buy an<br>EEPROM programmer to<br>make setting it up easier.<br>Right now, without one, it<br>will be extremely |

|----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |     | error-prone to set it up.                                                                                                                                  |

# 3.6 Personnel Effort Requirements

Include a detailed estimate in the form of a table accompanied by a textual reference and explanation. This estimate shall be done on a task-by-task basis and should be the projected effort in the total number of person-hours required to perform the task.

| Job                   | Textual Reference                                      | Explanation                                                                                                                                                                                                                                                                       | Hour Estimate |

|-----------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Instruction<br>Memory | Location to store instructions.<br>64x16 bit addresses | The instruction memory is<br>where the i281 will hold the<br>currently executed code. This<br>code is written in binary and<br>uploaded to an EEPROM that<br>can hold data offline. When<br>powered on, the EEPROM will<br>upload the required program to<br>a set of SRAM chips. | 20            |

| Registers             | Location to store current data.<br>4x8 bit addresses   | Registers are used for quick<br>data access. If a mathematical<br>function is occurring, the<br>registers will be accessed. The<br>i281 CPU utilizes 4 registers.                                                                                                                 | 20            |

| OpCode<br>Decoder     | Instruction to control<br>operation                    | The OpCode Decoder takes an<br>instruction and decides which<br>mathematical function is<br>expected to occur. The decoder<br>will utilize a set of control bits<br>to tell the ALU which actions<br>to perform                                                                   | 20            |

| ALU                   | Control of desired math function                       | The ALU is like the calculator<br>of a CPU. It takes two values<br>and does a mathematical                                                                                                                                                                                        | 20            |

|                   |                                                                       | operation on the values<br>dependent upon the OpCode<br>Decoder                                                                                                                                               |     |

|-------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Flags             | Detects irregularities in the ALU                                     | Flags are used inside the ALU<br>to detect certain irregularities.<br>These flags let the user know<br>when an unwanted value is<br>created and the operator can<br>take action if needed.                    | 10  |

| Control           | Adjusts flow of data for each instruction                             | The control changes the<br>direction of data flow<br>depending upon the desired<br>operation. It is in charge of<br>making sure the right data gets<br>to the right location.                                 | 20  |

| 7x Muxes          | Used to select between which<br>data will be used at<br>intersections | Multiplexers are controlled by<br>the control to tell data where to<br>go. Multiplexers can be seen as<br>"on-ramps" for an interstate.<br>Multiplexers make sure data<br>doesn't crash into other data.      | 20  |

| Data<br>Memory    | long-term storage of data                                             | Data memory is long-term<br>memory. If you don't want to<br>use a value immediately, it can<br>be stored in data memory. The<br>data memory can be accessed<br>later on if a value needs to be<br>referenced. | 20  |

| Display           | Show current values of memory                                         | Display is used to show values<br>inside the data memory. This<br>helps the user visualize the<br>current actions being taken on<br>the CPU.                                                                  | 40  |

| EEPROM<br>Program | Used as a microchip when needed                                       | The EEPROM will be used to<br>store code. This code will later<br>be uploaded to the CPU during<br>usage to run a program.                                                                                    | 20  |

| KiCad             | Created a PCB for<br>manufacturing                                    | KiCad is used to design a PCB.<br>KiCad is a free software. This<br>software has a large learning                                                                                                             | 120 |

| Total:    |                                        |                                                                                                                                                                       | 450 Hours |

|-----------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Other     | Ordering, implementation, testing      | Unknown issues may arise<br>during the implementation of<br>the i281 CPU. We will create<br>another category to give our<br>team wiggle room when an<br>issue arises. | 40        |

| Soldering | Attached desired modules to<br>the PCB | When the PCB arrives, we will<br>need to attach various<br>components. Soldering is a<br>strenuous task that will take<br>time to complete.                           | 80        |

|           |                                        | curve which will need to be<br>learned in order to design the<br>i281 CPU onto a PCB.                                                                                 |           |

# 3.7 Other Resource Requirements

Identify the other resources aside from financial (such as parts and materials) required to complete the project.

| Resource         | Description                                                                                                                                                                                   |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>Ben Eater</u> | Online resource about the design of 8 bit computers on breadboards.                                                                                                                           |

| <u>CprE 281</u>  | Our project is based on the i281 CPU created during CprE 281. We will utilize the notes, simulations, software, and code from this class to create a working product.                         |

| ETG              | The ETG will be our go-to for any<br>miscellaneous parts. These parts will be<br>used to implement the i281 CPU. Any parts<br>that are out of stock can be purchased via a<br>purchase order. |

| <u>Digikey</u>   | Digikey provides a variety of chips, tools,<br>controllers, and other equipment that might<br>be necessary for the project.                                                                   |

# 4 Design

## 4.1 Design Context

## 4.1.1 Broader Context

Describe the broader context in which your design problem is situated. What communities are you designing for? What communities are affected by your design? What societal needs does your project address?

Our project is designed for students and faculty. We want to make the life of the faculty and students easier and help future students learn and grow in the field of Computer Engineering. We want to give faculty members the ability to share their knowledge without having to spend extra time creating class material. We also want every student to feel accomplished and every faculty member to feel proud of their students. As a result, our project is focused on improving CprE 281 and the education of the students who take that class. This will, ideally, elevate the quality of engineers graduating from Iowa State due to an improved education in a core class.

| Area                                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Area<br>Public health,<br>safety, and<br>welfare | How does your project affect the general<br>well-being of various stakeholder groups?<br>These groups may be direct users or may<br>be indirectly affected (e.g., solution is<br>implemented in their communities)<br>Our project directly affects the well-being<br>of students, our shareholders, due to that<br>being directly correlated with the<br>educational quality of the lab section of<br>the class CprE 281. This is because our<br>project is focused on improving the labs in<br>CprE 281 by implementing Dr. Stoytchev's<br>i281 CPU in real life. By bringing this CPU<br>to life, Dr. Stoytchev aim's to have<br>students use it to better learn about the<br>subject. This affects both the quality of the<br>lab section of Dr. Stoytchev's CprE 281 | -Taking time to analyze desired<br>learning outcomes for students.<br>-Taking time to analyze clear ways<br>to display important concepts.<br>-Taking time to cleanly design the<br>layout so that it looks respectable<br>to those using our CPU.<br>-Limiting complexity by clearly<br>labeling individual components.<br>-Limiting confusion by using<br>LEDS to show progression of<br>execution.<br>By taking into consideration these<br>examples of how our project aims<br>to improve the quality of these<br>labs, we can reach this design goal. |

|                                                  | course and the quality of the education of the undergraduates in that course.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Global,<br>cultural, and<br>social               | How well does your project reflect the<br>values, practices, and aims of the cultural<br>groups it affects? Groups may include but<br>are not limited to specific communities,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | By building this CPU, we are<br>striving to improve the curriculum<br>in the lab section of CprE 281.<br>This reflects positively on the                                                                                                                                                                                                                                                                                                                                                                                                                   |

List relevant considerations related to your project in each of the following areas:

|               | nations, professions, workplaces, and<br>ethnic cultures.<br>Our project reflects not upon any specific<br>cultural group, per se, however it does<br>reflect upon the academic standards that<br>Iowa State University holds high. This is<br>because this project will directly impact<br>the educational quality of a core class in<br>the computer and electrical engineering<br>curriculum, and as a result, it affects the<br>Iowa State community as a whole. In our<br>effort to improve the curriculum, it<br>positively reflects the culture of the<br>university which strives for excellence.                                                                                                                                                                                                                          | values of Iowa State which strives<br>for excellence. Examples of this<br>improving students lives are:<br>-Students get to see how what they<br>learn in class is relevant to future<br>material.<br>-Students get to see digital logic in<br>action through the execution of<br>programs.<br>-Students get to see physical<br>versions of the different<br>components that comprise the<br>CPU they learn about in class.<br>-Students will be able to better<br>understand the material in class<br>with the physical version which<br>positively reflects on Iowa State's<br>values.                                                                                           |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Environmental | What environmental impact might your<br>project have? This can include indirect<br>effects, such as deforestation or<br>unsustainable practices related to materials<br>manufacture or procurement.<br>This project should have no discernable<br>environmental impact. While it uses metals<br>involved in circuitry (which can be hard to<br>acquire and lead to pollution in their<br>production), we are only developing one<br>breadboard implementation of this CPU<br>and are only producing one final PCB at<br>the end of the class. Additionally, the<br>power draw that this system will require to<br>run will be relatively low. As a result, this<br>won't cause excess pollution in the way of<br>power plants increasing the supply of<br>energy. This means our project has little to<br>no environmental impact. | <ul> <li>This system will require less<br/>power than the average lamp to<br/>run.</li> <li>We only need to build a single<br/>system, so the amount of parts we<br/>are sourcing (and their<br/>environmental footprint) is limited.</li> <li>This system has no plans to be<br/>mass produced, preserving our<br/>limited environmental impact.</li> <li>The parts we require are not do<br/>not involve super rare metals,<br/>although their continued mining of<br/>what we do need, industry-wide,<br/>does have an environmental<br/>impact. However, as previously<br/>stated, we barely impact that trade<br/>with the limited amount of parts<br/>we require.</li> </ul> |

| Economic      | What economic impact might your project<br>have? This can include the financial<br>viability of your product within your team<br>or company, cost to consumers, or<br>broader economic effects on communities,<br>markets, nations, and other groups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -Lab maintenance costs will be<br>reduced through more limited use<br>of FPGAs<br>-PCBs (should the one we produce<br>get damaged) are significantly                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| This project will significantly reduce the costs of maintaining the i281 lab for students. The current lab uses FPGA boards which can cost upwards of \$1,000 each. A PCB will cost <sup>1</sup> / <sub>4</sub> the price of an FPGA. This means that replacing the hardware that breaks each year will be a significantly reduced cost that can be used elsewhere. Additionally, this reduced cost could result in a lower technology fee for | cheaper to reproduce then a new<br>FPGA would be if damaged.<br>-Student lab/technology fees<br>should be reduced as a result<br>These impacts are rather positive<br>impacts for Iowa State and its<br>computer engineering department. |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| students taking that class.                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                          |

#### 4.1.2 User Needs

List each of your user groups. For each user group, list a needs statement in the form of:

User group needs (a way t0) do something (i.e., a task to accomplish, a practice to implement, a way to be) because some insight or detail about the user group

The CprE 281 students need the physical i281 CPU because it will help them visualize a datapath of a processor, and help them connect the dots on the basics they have been learning. Because they might use this for a lab the processor must be reprogrammable.

Statements for users:

Dr. Stoytchev: Dr. Stoytchev needs a way to teach his students i281 because he cares about his students and their knowledge.

281 Students: 281 Students need a way to visualize the components of a CPU because it will help them better understand how their class material is used in the world.

#### 4.1.3 Prior Work/Solutions

Include relevant background/ literature review for the project

- If similar products exist in the market, describe what has already been done

The current solution to demonstrate our project to students is through loading the design onto an FPGA (Field Programmable Gamma Array). FPGAs are highly specific computers that can be designed to implement a niche set of functions. However, FPGAs are quite expensive and have a very steep learning curve.

- If you are following previous work, cite that and discuss the advantages/shortcomings

The previous work we have been following for implementing this system on breadboards is through a youtube series by Ben Eater. <u>https://youtu.be/HyznrdDSSGM</u>

The problem with Ben's work is that each instruction of the computer takes multiple clock cycles. The computer we are attempting to implement will utilize only one cycle/instruction. This means that we will have to redesign the bus system and other control components to run on a single clock cycle, a problem that is much easier said than done to fix.

- Note that while you are not expected to "compete" with other existing products / research groups, you should be able to differentiate your project from what is available. Thus, provide a list of pros and cons of your target solution compared to all other related products/systems.

| Competitor Pros                                                                         | Competitor Cons                                                       |

|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| <ul><li>Large Quantity Available</li><li>Efficient</li><li>Looks Professional</li></ul> | <ul><li> Price</li><li> Fragile</li><li> Hard to Understand</li></ul> |

| Our Project Pros                                                                           | Our Project Cons                                        |

|--------------------------------------------------------------------------------------------|---------------------------------------------------------|

| <ul><li>Easy to Follow</li><li>Cheap</li><li>Reprogrammable</li><li>Redesignable</li></ul> | <ul><li>Inefficient</li><li>Hard to Replicate</li></ul> |

#### 4.1.4 Technical Complexity

Provide evidence that your project is of sufficient technical complexity. Use the following metric or argue for one of your own. Justify your statements (e.g., list the components/subsystems and describe the applicable scientific, mathematical, or engineering principles)

1. The design consists of multiple components/subsystems that each utilize distinct scientific, mathematical, or engineering principles –AND–

2. The problem scope contains multiple challenging requirements that match or exceed current solutions or industry standards.

The current design can be broken down into several sub-components including the ALU, fetch logic, register file, data memory, and instruction memory. The ALU requires the ability to add, subtract, and shift. The fetch logic must be able to increment the program counter of the processor for normal instructions, in addition to executing branch operations. The instruction memory and data memory will need to be programmable, which will require the addition of a microcontroller.

In addition to the multiple components present in our project, the project itself can be broken down into multiple subprojects. The first subproject that must be completed in the construction of a breadboarded prototype of the processor. This will require extensive research of chips and careful design considerations for propagation and power requirements. The next subproject involves the design of a PCB, which will require software like KiCad to complete. The third subproject is the creation of an assembler to upload instruction files onto the processor. Considering all of these factors we believe that the project possesses the appropriate level of complexity to be considered for an ABET-accredited senior design.

## 4.2 DESIGN EXPLORATION

#### 4.2.1 Design Decisions

List key design decisions (at least three) you have made or will need to make in relation to your proposed solution. These can include but are not limited to, materials, subsystems, physical components, sensors/chips/devices, physical layout, features, etc.

Decision 1: LED choice. The first major decision our team faced was implementing LEDs into the CPU design. LEDs are a great way to visualize data flow in a system. However, LEDs draw lots of power and create an extra footprint that will need to be accounted for. We decided to test a large set of LEDs to find the lowest power devices we could. Next, we decided that each bus only needs a single set of LEDs instead of implementing LEDs on each module.

Decision 2: Communication method: The second issue we struggled with was communication. At the start of the semester, we tested the water with 4 different communication methods. This was great because we were always connected as a team. When we started creating files for our project it was a trainwreck to look in 4 locations to find the file you desired. We ended up agreeing on Google Drive for data sharing and discord for group communication.

Decision 3: Memory Device. The third decision our team is still struggling with is how to implement memory. During each team meeting, we end up generating more ideas than we can handle. Although these new ideas are great, it hasn't made the decision easier. We

hope to come to a conclusion within the next two weeks so we can order the parts required for our memory systems.

#### 4.2.2 Ideation

For one design decision, describe how you ideated or identified potential options (e.g., lotus blossom technique). List at least five options that you considered.

The design decision we are going to focus on is the memory device. The way we went about comparing each device is by using a pros and constable. We create a presentation showing each device we considered using. Each slide highlighted a different device that was considered. This method made it very easy for our team to meet with multiple groups of people to get recommendations. Along the way we revised our presentation before showing it to our client. Our client really enjoyed this method.

The list of devices we considered is as follows:

- EPROM

- EEPROM

- Flash

- Static Memory

- DRAM

- SRAM

- ROM

- Raspberry PI

- Registers

#### 4.2.3 Decision-Making and Trade-Off

Demonstrate the process you used to identify the pros and cons or trade-offs between each of your ideated options. You may wish to include a weighted decision matrix or other relevant tool. Describe the option you chose and why you chose it.

As we previously stated the way we compared each device was via a presentation of pros and cons tables. We chose this to help our client understand what we were dealing with. This method broke each option into a simple to follow explanation. Our client didn't have much knowledge on data types so we wanted them to get the most out of our research. This presentation was a great way to get advice on each device from faculty members and other students. No one person is an expert in every memory type, but some people are extremely well versed in a single type of memory. Presenting only one type of memory to these experts helped us collect critical data without any misinformation.

#### 4.3 PROPOSED DESIGN

#### Discuss what you have done so far – what have you tried/implemented/tested?

So far, we have constructed a register file, ALU, and memory. We have attempted implementation of a program counter, but that failed on the first attempt. The ALU, register file, and memory have been extensively tested.

#### 4.3.1 Design Visual and Description

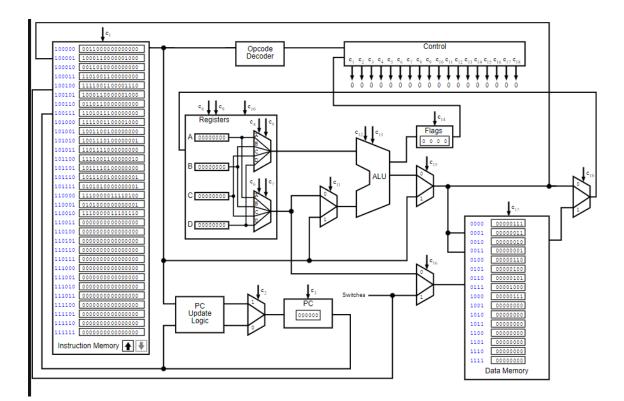

Include a visual depiction of your current design. Different visual types may be relevant to different types of projects. You may include: a block diagram of individual components or subsystems and their interconnections, a circuit diagram, a sketch of physical components and their operation, etc.

Describe your current design, referencing the visual. This design description should be in sufficient detail that another team of engineers can look through it and implement it.

This is the data flow of the I281 CPU. The data flow consists of decoding instruction memory, changing control signals, and doing arithmetic. This visual provides the general layout of the I281 CPU, with lines that demonstrate the paths and connections that are needed between each component.

#### 4.3.2 Functionality

Describe how your design is intended to operate in its user and/or real-world context. This description can be supplemented by a visual, such as a timeline, storyboard, or sketch.

How well does the current design satisfy functional and non-functional requirements?

The computer/processor will be able to take in machine code assembled by a custom assembler created by us. The processor will then process those instructions and output the current program being run on 7-segment displays or LEDs.

Our current design appears to satisfy all requirements laid out for us to meet.

## 4.3.3 Areas of Concern and Development

Based on your current design, what are your primary concerns for delivering a product/system that addresses requirements and meets user and client needs?

Our largest concerns for delivering a product are time constraints. Our project is to build an entire computer on breadboards. We estimated that our project will take over 400 hours to fully complete. Our team cannot guarantee that we can spend 400 hours to complete this project. We will need to find a way to make cuts in time to produce a CPU for our client.

What are your immediate plans for developing the solution to address those concerns? What questions do you have for clients, TAs, and faculty advisers?

One of the largest time consumptions we have run into thus far is waiting for parts to arrive. We have started to plan each module well in advance of implementation to ensure we don't have downtime while waiting for parts to come in. At this point we have a large surplus of parts and have worked with the ETG to understand what is readily available for us to use.

## 4.4 Technology Considerations

Highlight the strengths, weaknesses, and trade-offs made in technology available.

| Data Memory<br>Technology | EEPROM                                                                                                                     | EPROM                                                                                                               |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Pros                      | <ul> <li>Can Be<br/>Reprogrammed</li> <li>Easy to Understand</li> <li>Compatible with<br/>EEPROM<br/>programmer</li> </ul> | <ul> <li>Cheap</li> <li>Easy to use</li> <li>Many sizes, Many<br/>Applications</li> <li>Widely Supported</li> </ul> |

| Cons                      | <ul> <li>Large Programming<br/>Learning Curve</li> <li>Few Design Style</li> </ul>                                         | • Cannot be<br>reprogrammed<br>during use                                                                           |

Discuss possible solutions and design alternatives

## 4.5 Design Analysis

- Did your proposed design from 3.3 work? Why or why not?

- What are your observations, thoughts, and ideas to modify or iterate over the design?

Our proposed design was intended to complete a single set of instructions without error. However, we have changed our design to include completing any program. This means that our data memory and instruction memory will need to be rewritable. These two components will be redesigned to allow for changes in the data state. This means that we will need to find a new way to store and write data.

#### 4.6 DESIGN PLAN

Describe a design plan with respect to use-cases within the context of requirements, modules in your design (dependency/concurrency of modules through a module diagram, interfaces, architectural overview), module constraints tied to requirements.

First we will implement all of the sub components on breadboards. After that we will create a dataflow with control signals on the breadboards. After we have a first dataflow, we will implement all required instructions. AFter this we will work on how to program the computer, and finally we will put the final design on the PCB and give it to the customer.

# 5 Testing

Testing is an extremely important component of most projects, whether it involves a circuit, a process, power system, or software.

The testing plan should connect the requirements and the design to the adopting test strategy and instruments. In this overarching introduction, given an overview of the testing strategy. Emphasize any unique challenges to testing for your system/design.

#### 5.1 UNIT TESTING

#### What units are being tested? How? Tools?

There are multiple subsystems of the CPU, including the data memory, register file, ALU, instruction memory, and control logic. Each of the subsystems of the CPU are tested individually using dip switches to emulate data from the register file/instruction memory. The way that we have tested these is setting the switches to a specific value and observing the LED indicators on the output of the unit (tools include oscilloscopes, multimeters, and LED indicators). This is the most concrete way to test our project because we already know what outputs to expect, so it just becomes a matter of verifying that our breadboard builds match our expectations.

# 5.2 INTERFACE TESTING

What are the interfaces in your design? Discuss how the composition of two or more units (interfaces) are being tested. Tools?

Our interface is switches, LED's, 7-segment displays, and the text interface used to write the assembly. First, the LED's and switches will be tested by programming our instruction memory (which has not been setup yet) with basic instructions to make sure the LED values are correct. Next, the 7-segment displays will be tested to ensure the proper hexadecimal values are output with the correct inputs. Finally, the assembler will be tested by checking the output binary file it produces (tools for this are primarily visual verification, other tools are currently unknown).

## 5.3 INTEGRATION TESTING

What are the critical integration paths in your design? Justification for criticality may come from your requirements. How will they be tested? Tools?

The integration of all subsystems of the CPU (ALU, Register File, Instruction memory, data memory, and control logic) will happen after all of them are completed. They will be slowly integrated to first make a basic data path that can do an add instruction. After the first datapath is completed more capability will be added to support more instructions until all of them are supported (tools include oscilloscopes, multimeters, and LED indicators).

# 5.3 System Testing

Describe system level testing strategy. What set of unit tests, interface tests, and integration tests suffice for system level testing? This should be closely tied to the requirements. Tools?

The system will be tested after all subsystems have been verified to work as intended. The testing will consist of creating a basic datapath and checking the LED indicators to ensure correct dataflow. If errors occur we shall use multimeters and oscilloscopes to debug problems.

# 5.4 Regression Testing

How are you ensuring that any new additions do not break the old functionality? What implemented critical features do you need to ensure they do not break? Is it driven by requirements? Tools?

All components are being tested individually before being fully integrated, so there is very little old functionality to break with new additions. When additions are made, they are made to individual components which we can test independently. What is very convenient about our project is that if the components work, the whole system should in theory work, so we know that when we connect the components together, there is very little risk that changing one component will break old components and their functionality. However, that said, each component is critical to the success of the project as a whole, and as a result of that, we need to ensure that our testing is incredibly thorough so find any issues with each component before we bring them all together. This testing is driven by the fact that CPU's require each of the components we are building, and we have been given a design by our client so we must follow it closely. Tools which we can utilize for this type of testing are primarily centered around LEDs which show us if our expected output is correct, which helps us verify if our components are correct and working properly. Additional tools we can use are oscilloscopes and multimeters for connection testing.

## 5.5 Acceptance Testing

How will you demonstrate that the design requirements, both functional and non-functional are being met? How would you involve your client in the acceptance testing?

Along with consistent meetings with our client to update him about the project, we also have a set list of requirements we created with the client. This keeps us on track by ensuring we know exactly what we need to do. During our weekly meetings, we demonstrate any progress, so if the client has any different requirements then we can change as we go.

## 5.6 Results

What are the results of your testing? How do they ensure compliance with the requirements? Include figures and tables to explain your testing process better. A summary narrative concluding that your design is as intended is useful.